In the realm of space electronics, reliability is paramount. Every component onboard a spacecraft must withstand the harsh conditions of outer space, including extreme temperatures, vacuum, and radiation. Among these components, Field-Programmable Gate Arrays (FPGAs) play a crucial role and come with their own set of challenges.

Challenges with FPGAs in Space

Two significant challenges that affect FPGAs are power management and susceptibility to radiation-induced failures.

Ensuring stable power to an FPGA in space is not a trivial task. With the trend towards lower core voltages and the use of multiple voltage rails, supervising and sequencing these power rails is essential to guarantee system reliability.

To understand the second challenge, we need to dig a bit into the FPGA microarchitecture.

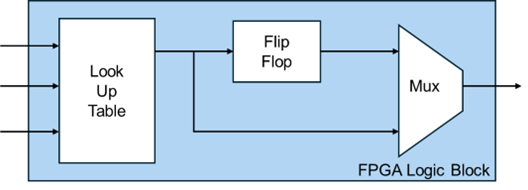

Look-Up Tables (LUTs) are the fundamental building blocks for implementing logic functions in a FPGA. A LUT typically consists of a small amount of memory that stores a truth table representing the desired logic function. This memory can be programmed to implement any arbitrary logic function of a fixed number of input signals. The memory that controls the behaviour of the LUT is called the FPGA configuration memory. The state of the configuration memory defines the logic function implemented in the FPGA fabric. For SRAM based FPGAs, the configuration memory is typically loaded from an external non-volatile memory after power-up and remains static until the system loses power.

Electronic devices operating in the space environment are susceptible to Single Event Effects (SEE) due to ionizing particles that may affect the system and generate errors. SRAM cells are highly vulnerable to radiation-induced errors because of their intrinsic programmability characteristics. SRAM-based FPGAs are, therefore, susceptible to errors that may affect not only the user data but also the configuration memory. Errors in the FPGA configuration memory are persistent during device operation and may affect the architectural behaviour of the implemented design, compromising the integrity of the entire system.

Single Event Latchup (SEL) is another type of radiation-induced failure mechanism. A SEL happens when a single energetic particle passes through sensitive regions of the device, triggering charge accumulation. These charges can create a low impedance path between power rails, leading the system to a very high current state. A SEL may result in catastrophic damage and permanent loss of functionality if no countermeasures are put into place.

The Solution: GR716B Space-Grade Microcontroller

The GR716B space-grade microcontroller addresses these challenges faced by FPGAs in space applications.

The GR716B includes a set of hardware blocks such as ADCs, DACs and smart PWM controllers that enable it to support and control multiple DC/DC converters. With these capabilities, the GR716B can be part of the power subsystem to ensure stable power delivery to the FPGA.

The GR716B can also detect Single Event Latch-up (SEL) occurring in an FPGA. By utilizing on-chip hardware components such as fast analog comparators, ADCs, and FIR filters, it can monitor with precision the FPGA power supply voltage and current. Any deviations from expected levels on these lines can be swiftly identified and remedied, averting potential failures and enhancing the reliability of the whole system.

Moreover, by integrating the GRSCRUB FPGA supervisor, the GR716B can also employ error mitigation techniques for SRAM-based FPGAs such as AMD Virtex5 and Kintex UltraScale.

GRSCRUB can continuously detect and correct radiation-induced errors (bit-flips) affecting the FPGA configuration memory. However, one must notice that, as any other scrubbing solution, GRSCRUB does not avoid bit-flips from happening or their effects on the design. Therefore, additional mitigation techniques at design level are recommended to decrease the number of single points of failure in the system and increase the fault masking. For example, in this RADECS 2022 paper, we have demonstrated the effects of using the GRSCRUB together with a distributed Triple Modular Redundancy (TMR) synthesis strategy.

GRSCRUB also enables reprogramming of the FPGA in flight. With this capability, missions can leverage the same hardware for multiple purposes, optimizing resource utilization and mission efficiency.

Summary

The GR716B space-grade microcontroller offers new capabilities as an FPGA supervisor. By addressing the challenges of power management and radiation-induced errors in FPGAs, the GR716B empowers space missions with enhanced reliability and flexibility.